# A single-phase synchronization technique for grid-connected energy storage system under faulty grid conditions

Komal Saleem, Graduate Student Member, IEEE, Zunaib Ali, and Kamyar Mehran, Senior Member, IEEE

Abstract -- The control of single-phase grid-connected Energy Storage System (ESS) requires a very fast and accurate estimation of grid voltage frequency and phase angle. A Phaselocked Loop (PLL) based synchronization algorithm usually extracts this information. The operation and control of entire system is directly affected by the performance of PLL. In this paper, a novel Advanced Single-phase PLL (ASoPLL) technique with reduced complexity is proposed for the fast and accurate extraction of grid information in a ESS under distorted and abnormal grid conditions including harmonics, interharmonics, DC-offset and grid faults. The proposed method provides a faster dynamic response, lower frequency overshoot, and accurate estimation under off-nominal grid frequencies with reduced computational complexity in comparison to the existing method. The advanced performance of the proposed AS\(\phi\)PLL is verified through simulation and experimental results.

Index Terms—Power quality, Phase-locked loop, current controller, harmonics, DC-offset, Energy Storage System.

#### I. INTRODUCTION

The increasing integration of single-phase grid-connected energy storage systems (including electric vehicles and renewable systems) give rise to various new grid codes and regulations to obtain high quality output power. The grid codes [1, 2], for example, include maintaining the frequency and voltage limits, providing necessary Fault Ride Through (FRT) support and injecting high quality power in the event of grid disturbances such as faults, interharmonics, frequency and phase variations etc. This is necessary in order to regulate more efficiently as well as to diversify the role and contribution of renewable energy and electric vehicular system on electrical grids [3, 4]. The key element for the efficient and reliable integration of such systems to the grid is the power electronic based Grid Side Converter (GSC) [5, 6]. Consequently, the proper design of GSC controller plays a vital role for the overall operation of grid connected stationary and mobile storage systems, and thus, it should be enhanced and diversified to meet the modern grid requirements.

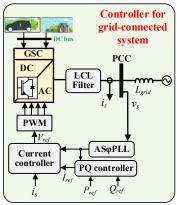

A typical block diagram for a single-phase grid-connected system is shown in Fig. 1 where electric vehicle and/or renewable energy is connected to GSC through DC bus. The

Komal Saleem and Kamyar Mehran are with the School of Electronic Engineering and Computer Science, Queen Mary University of London, UK (email: <a href="mailto:k.saleem@qmul.ac.uk">k.mehran@qmul.ac.uk</a>). Zunaib Ali is currently working as Research Fellow at Northumbria University, Newcastle, UK (email: zunaib.ali@northumbria.ac.uk)

GSC controller comprises of two sub-controllers and a synchronization unit. The sub-controllers include an active/reactive (PO) controller to generate the reference currents based on the desired P and Q, and a current controller to ensure the accurate injection of these currents into the grid. The synchronization unit, known as the heart of control system, is responsible for extracting the grid voltage information (that is, frequency, phase and amplitude) required for synchronization and control purposes (especially in dqsynchronous domain). The widely used synchronization method is the Phase-Locked Loop (PLL) algorithm [5, 7, 8]. Since the operation of both PQ and current controller is directly affected by the performance of synchronization unit, the accurate operation of GSC is heavily dependent on the proper design of PLL. In addition to accurate performance, the complexity of PLL is also very important as in real-time the embedded microcontrollers (having limited available processing resources) are used to develop the GSC control system [5, 9]. If the complexity is relatively high, these microcontrollers cannot be operated in real-time at a given sampling rate. It is, therefore, necessary to design such control units with the least computational burden [10]. Thus, in this paper, a novel less complex synchronization technique has been proposed for the accurate extraction of grid information under distorted and abnormal grid conditions.

Several single-phase PLLs exist in the literature but with certain pros and cons. A common approach used for the development of single-phase PLLs is to generate the inquadrature voltage vector  $(\mathbf{v}_{\alpha\beta})$  using the grid voltage  $(v_g)$ . The voltage vector is then transformed to the  $dq^{+1}$  rotating reference frame  $(\mathbf{v}_{dq}^{+1})$  and the resulting  $v_q^{+1}$  is provided to the Phase Detector (PD) part of the PLL to extract the grid voltage phase angle  $(\theta_a)$ . In this way, the Quadrature Signal Generator (OSG) and the rest of processing contribute to the overall design of a single-phase PLL. The simplest single-phase PLL is the T/4 Delay technique [12], in which, the quadrature signal is generated by delaying the grid voltage with a factor of T/4 (where, T is the grid's fundamental period). This technique, however, suffers from inaccuracies under grid voltage harmonics, interharmonics and DC-offset. The Inverse Part Transformation (IPT) PLL [13, 14] uses back-to-back connection of stationary and rotating reference frame transformations and Low Pass Filters (LPF) to generate the inphase and quadrature signals. This configuration forms a second-order band pass filter and attenuate the higher order harmonics. However, the low order harmonics/interharmonics are not compensated and also the filtering capability for higher order harmonics is not significant. Interesting synchronization methods, including the Second Order Generalized Integrator (SOGI) based PLL and Frequency-Locked Loop (SOGI-FLL),

The paper's conference version has been presented at the 2019 IEEE Energy Conversion Congress and Exposition, Baltimore, MD, USA, 29 Sept.-3 Oct. 2019 [11]. (Corresponding author: Komal Saleem)

Komal Saleem is grateful to Higher Education Commission (HEC) Pakistan and Queen Mary University of London for providing PhD Scholarship and financial assistance.

and adaptive filter based Enhanced PLL (EPLL) with performance similar to the IPTPLL are discussed in [5, 12-17]. SOGIPLL and SOGIFLL provides immunity against harmonics (high order only) due to low/band pass filtering characteristics and fast dynamics under grid faults, however, low order harmonics cannot be adequately removed [13]. The EPLL according to [14] presents poor immunity against high as well as low harmonics and suffers from slow dynamics compared to SOGIPLL.

A Hilbert transform based PLL [18] achieves accurate phase angle estimation under grid voltage harmonics. However, applying it practically on time dependent signals imposes implementation problems. The authors in [19] proposed two PLL techniques named as the Enhanced Transfer Delay PLL (ETDPLL) and Non-frequency dependent Transfer Delay PLL (NTD-PLL). The two PLLs use small signal model-based transport delay and input gains for the compensator and improve the synchronization response. However, as discussed in [19], they still lack in complete elimination of oscillations caused by harmonics. The inaccurate response of the PLL under harmonics affect the power quality of grid-connected converter because the operation of GSC controller (including the reference frame transformations) is heavily dependent on the synchronization algorithm.

For immunity against harmonics, several techniques have been suggested, including the multi-resonant and repetitive controllers [20], in-loop Moving Average Filters (MAF) [21] [22] and adaptive or notch filters [23], [24]. The compensation of harmonics is achieved using these methods, however, degrade the dynamic response of the PLL as discussed in [5], [25] for the MAF based PLLs. Recently the dynamic response of MAF based PLL has been improved in [26, 27] with proposing to move the MAF outside of control loop and incorporate it in the pre-filtering stage, along with necessary improvements to the phase error under off-nominal grid frequency. Even though the dynamic response is improved compared to conventional in-loop MAF, the improvement seems inconsequential when compared to non-MAF PLLs.

It is important that the synchronization technique possess DC-offset rejection capability as the presence of DC in the grid voltage appears as low frequency oscillations in the frequency and phase error estimation. The method proposed in [28] uses tuning procedure to adjust the bandwidth of synchronization technique for the compensation of DC-offset, however, it suffers from slow dynamic response. The integration based technique for the mitigation of DC-offset is presented in [29]. In addition to complex implementation, this method also suffers from degraded dynamic response.

A LPF is added in a QSG based SOGI-PLL in [30] results in the rejection DC-offset but only from quadrature component. The author in [31] rearranged the structure presented in [30] with addition of some mathematical operations in order to fully remove the DC-offset from  $\beta$ -component, however the technique proposed does not work for higher order harmonics. In order to remove the drawbacks of [30] [31] the authors in [16] proposed a cascaded SOGI-PLL,

which results in complete elimination of DC-offset from orthogonal signals. In [32], in addition to DC-offset rejection the authors tuned a set of QSG based SOGI for selective harmonic elimination. The new combination removes predefined harmonics in addition to DC-offset but at the same time design's complexity is increased. The author proposed an all pass filter based SOGI-PLL in [33] which removes DC-offset and also worked for frequency and fault variations with low complexity. However, in case of harmonic elimination, the total harmonic distortion is more than the provided maximum limit for grid connected systems.

A PLL technique has been proposed in [34], [35] for the compensation of selected low-order harmonics using Multi-Harmonic Decoupling Cells (MHDC). The estimated quantities by MHDCPLL are subject to oscillations under off nominal grid frequency and presents high frequency overshoot in the event of faults. Moreover, it requires large number of Park transformations, which in turn increases the computational complexity. There are other limitations such as requiring prior knowledge of individual harmonic to be compensated (as it is tuned to specific harmonics) and lack of accuracy in the compensation of interharmonics (especially the ones close to the fundamental frequency).

To address the aforementioned limitations of existing PLL techniques, a novel Advanced Single-phase PLL (AS $\phi$ PLL) is proposed in this paper. The proposed AS $\phi$ PLL compensates for grid voltage harmonics, interharmonics, DC-offset and faults with accuracy and fast dynamic response. It is also immune to off-nominal frequency oscillations and presents lower frequency overshoot. Most importantly, the proposed PLL algorithm is less complex and does not require prior knowledge of which harmonics to be compensated. Therefore, the proposed AS $\phi$ PLL is the most suitable candidate for grid-connected energy storage systems allowing bi-directional flow of high-quality power under distorted and faulty grid conditions.

The rest of the paper is structured as follows: The design of proposed and existing PLLs is presented in section II followed by the tuning of the PLLs in section III. computational complexity analysis carried out in section IV. The validation of proposed technique with simulation and experimental results are outlined in section V. After validating the frequency and phase estimation of proposed PLL for several grid disturbances, Section VI demonstrates the impact of proposed synchronization technique on the overall operation of grid-connected system. The paper concludes in Section VII.

#### II. THE PROPOSED AND EXISTING PLLS

This section presents in detail the structure of proposed PLL, its schematic diagram, design methodology and mathematical analysis. In addition, short description of SOGIPLL and MHDCPLL along with their diagrams are also added as they will be used in the later section for comparison.

#### A. The Proposed Advanced Single-Phase PLL (ASφPLL)

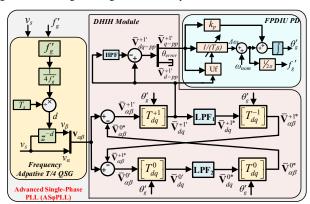

The proposed PLL is designed in the dq- rotating reference frame and a combination of various blocks, including the QSG,

the DC-offset and Harmonic-Interharmonic (DHIH) compensation module, and the adaptive PD. The QSG is used to generate the in-quadrature voltage vector  $\mathbf{v}_{\alpha\beta}$  and is adaptive to frequency variations. The DHIH is to cancel out the effect of DC-offset and harmonics/interhamronics present in the grid voltage, resulting in oscillations free  $dq^{+1}$  voltage vector. Subsequently, the  $q^{+1}$ -component is processed by the phase detector to estimate the phase  $(\theta'_g)$  and frequency  $(f'_g)$  of grid voltage.

Fig. 1: Control diagram for grid connected system.

Fig. 2: The block diagram of the proposed ASφPLL.

#### Quadrature Signal Generator (QSG)

The QSG is formed by the frequency adaptive implementation of T/4 delay transportation to generate the inquadrature voltage vector  $\mathbf{v}_{\alpha\beta}$ , where T represents the fundamental period of the grid voltage. In this method, the inphase component (i.e.  $v_{\alpha}$ ) is obtained by passing the input grid voltage  $v_g$  with a unity gain, whereas the quadrature component  $(v_{\beta})$  is generated by quarterly delaying the input voltage, as shown in Fig. 2 and mathematically represented in (1).

$$\mathbf{v}_{\alpha\beta} = \begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \begin{bmatrix} v_{s} \\ v_{s} z^{-d} \end{bmatrix} \tag{1}$$

The frequency adaptation is achieved by providing the estimated grid frequency as a feedback to QSG to generate the required transportation delay (d) of quarter period, resulting in the quadrature component. The d required for implementation

of frequency adaptive T/4 is calculated using (2), where  $T_s$  is the sampling rate of GSC controller, as depicted in the Fig. 2.

$$d = \left(\frac{T}{4}\right)T_s = \left(\frac{1}{4f_g'}\right) \div T_s \tag{2}$$

The QSG may results in inaccuracies for the case when d is a non-integer. For such a case, the d is divided into two parts, integer and fractional order delay. The integer part can be directly used by the controller, while the other part is solved using Lagrange Interpolation [36].

#### DC-Offset and Harmonic-Interharmonic (DHIH) Compensation Module

The main objective of this paper is to enable a less complex, fast and accurate estimation of grid voltage phase and frequency under grid voltage DC-offset and harmonics/interharmonics. The single-phase grid voltage  $v_g$  consisting of fundamental component  $(v^1)$ , DC-offset  $(v^0)$ , harmonics  $(\Sigma v^h)$  and interharmonics  $(\Sigma v^{ih})$  is expressed as:

$$v_s = v^1 + v^0 + \sum v^h + \sum v^{ih}$$

(3)

The resulting in-quadrature vector  $\mathbf{v}_{\alpha\beta}$  at the output of QSG given in (4) contains all the voltage components mentioned in (3), where n=1 represents the fundamental component and n=3,5,7,9,... represents harmonics.

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = V^{1} \begin{bmatrix} \cos(\omega t + \theta_{1}) \\ \cos(\omega \left(t - \frac{T}{4}\right) + \theta_{1}) \end{bmatrix} + \underbrace{\begin{bmatrix} v_{\alpha}^{0} \\ v_{\beta}^{0} \end{bmatrix}}_{Dc - offset}$$

$$+ \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega \left(t - \frac{T}{4}\right) + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega \left(t - \frac{T}{4}\right) + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega \left(t - \frac{T}{4}\right) + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t + \theta_{n}) \end{bmatrix}}_{Harmonics} + \underbrace{\sum_{n=3,5,7,9,\dots} V^{n} \underbrace$$

Equation (4) can be rewritten as below:

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = V^{1} \begin{bmatrix} \cos(\omega t + \theta_{1}) \\ \cos(\omega t - \frac{\pi}{2} + \theta_{1}) \end{bmatrix} + \begin{bmatrix} v_{\alpha}^{0} \\ v_{\beta}^{0} \end{bmatrix} + \sum_{n=3,5,7,9,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos(n\omega t - \frac{n\pi}{2} + \theta_{n}) \end{bmatrix} + \sum_{i=3,5,7,9,\dots} \mathbf{v}^{ih}$$

(5)

Solving (5), the harmonics can be divided in the form of positive and negative set of harmonics, as described by (6).

$$\begin{bmatrix}

v_{\alpha} \\

v_{\beta}

\end{bmatrix} = V^{1} \begin{bmatrix}

\cos(\omega t + \theta_{1}) \\

\sin(\omega t + \theta_{1})

\end{bmatrix} + \begin{bmatrix}

v_{\alpha}^{0} \\

v_{\beta}^{0}

\end{bmatrix} + V^{n} \begin{bmatrix}

\sum_{n=3,7,11,\dots} \begin{bmatrix}

\cos(n\omega t + \theta_{n}) \\

\cos(n\omega t - \frac{3\pi}{2} + \theta_{n})\end{bmatrix} + \\

\sum_{n=5,9,13,\dots} \begin{bmatrix}\cos(n\omega t + \theta_{n}) \\

\cos(n\omega t - \frac{\pi}{2} + \theta_{n})\end{bmatrix} + V^{n} \end{bmatrix} + V^{n} V^{$$

Equation (6) can be transformed to (7) by using basic trigonometry as below:

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = V^{1} \begin{bmatrix} \cos(\omega t + \theta_{1}) \\ \sin(\omega t + \theta_{1}) \end{bmatrix} + \begin{bmatrix} v_{\alpha}^{0} \\ v_{\beta}^{0} \end{bmatrix} + V^{n} \begin{bmatrix} \sum_{n=3,7,11,\dots} \begin{bmatrix} \cos(-n\omega t - \theta_{n}) \\ \sin(-n\omega t - \theta_{n}) \end{bmatrix} + \sum_{n=5,9,13,\dots} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \sin(n\omega t + \theta_{n}) \end{bmatrix} + \sum_{n=5,9,13,\dots} \mathbf{v}^{ih}$$

(7)

The generalized equation for  $v_{\alpha\beta}$  is depicted in (8)

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = V^{1} \begin{bmatrix} \cos(\omega t + \theta_{1}) \\ \sin(\omega t + \theta_{1}) \end{bmatrix} + \begin{bmatrix} v_{\alpha}^{0} \\ v_{\beta}^{0} \end{bmatrix} + V^{n} \left( \sum_{n=3,7,1,1} \begin{bmatrix} \cos(\psi(n\omega t + \theta_{n})) \\ \sin(\psi(n\omega t + \theta_{n})) \end{bmatrix} \right) + \sum \mathbf{v}^{ih}$$

(8)

where,

$$\psi = \begin{cases} +1 & for \ n = 5,9,13, \dots \\ -1 & for \ n = 3,7,11, \dots \end{cases}$$

The proposed PLL is designed in the dq-frame, which however, results in unwanted oscillations when the input signal with more than one frequency is transformed with a specific angular speed, as can be realized from (9). The n in (9) represents the dq-frame under consideration and m holds all other values except n. Thus, we must cancel out the effect of oscillations from the transformed voltage vector and achieve a clean fundamental voltage vector  $\mathbf{v}_{dq}^{+1}$  for the estimation of the grid angle and frequency.

$$\mathbf{v}_{dq}^{n} = \left[\mathbf{T}_{dq}^{n}\right]\mathbf{v}_{\alpha\beta} = \underbrace{\mathbf{V}_{dq}^{n}}_{non-oscillating} + \underbrace{\sum_{m \neq n} \left\{\mathbf{V}_{dq}^{m}\left[\mathbf{T}_{dq}^{n-m}\right]\right\}}_{Oscillating terms}$$

(9)

where,  $\mathbf{V}_{dq}^n$  is the DC term (non-oscillating) for the  $n^{\text{th}}$  rotating frame,  $\mathbf{V}_{dq}^m$  is the amplitude of  $m^{\text{th}}$  frequency component of the oscillating term and  $[\mathsf{T}_{dq}^n]$  is used to transform the input vector to corresponding dq-frame and is given in (10) with  $\theta$  being the PLL angle.

$$\begin{bmatrix} T_{dq}^n \end{bmatrix} = \begin{bmatrix} \cos(n\theta) & \sin(n\theta) \\ -\sin(n\theta) & \cos(n\theta) \end{bmatrix}$$

(10)

The proposed DHIH module in this work comprises of a DC elimination block and a harmonic/interharmonic compensation unit. The DC block is developed using a mathematical cancellation scheme for the fast and accurate compensation of grid voltage DC-offset. The mathematical cancelation is required because oscillations resulting from DC-offset have low frequency in the dq- frame. The HIH unit, on other hand, takes DC compensated signal as the input and clear it from the effect of harmonics and interharmonics.

While developing DC-offset compensation block, the effect of harmonics and interharmonics are not considered, and will be compensated later using the proposed HIH unit. Then, using (9), the dq-transformed voltage vectors for n = +1 (fundamental) and n = 0 (DC-offset) is obtained as in (11).

$$\begin{bmatrix} \mathbf{v}_{dq}^{+1} \\ \mathbf{v}_{dq}^{0} \end{bmatrix} = \underbrace{\begin{bmatrix} \overline{\mathbf{V}}_{dq}^{+1} \\ \overline{\mathbf{V}}_{dq}^{0} \end{bmatrix}}_{DC \ terms} + \underbrace{\begin{bmatrix} [0] & [T_{dq}^{+1-(0)}] \\ [T_{dq}^{0-(+1)}] & [0] \end{bmatrix} \begin{bmatrix} \overline{\mathbf{V}}_{dq}^{+1} \\ \overline{\mathbf{V}}_{dq}^{0} \end{bmatrix}}_{oscillating \ terms}$$

(11)

It can be seen that the desired voltage vector  $\mathbf{v}_{dq}^{+1}$ , in addition to DC term  $\overline{\mathbf{V}}_{dq}^{+1}$ , suffers from fundamental frequency oscillations appearing because of DC-offset. Consequently, oscillations are decoupled by rewriting (11) as (12).

$$\begin{bmatrix} \overline{\mathbf{V}}_{dq}^{+1} \\ \overline{\mathbf{V}}_{dq}^{0} \end{bmatrix} = \begin{bmatrix} \mathbf{v}_{dq}^{+1} \\ \mathbf{v}_{dq}^{0} \end{bmatrix} - \begin{bmatrix} [0] & [T_{dq}^{+1-(0)}] \\ [T_{dq}^{0-(+1)}] & [0] \end{bmatrix} \begin{bmatrix} \overline{\mathbf{V}}_{dq}^{+1} \\ \overline{\mathbf{V}}_{dq}^{0} \end{bmatrix}$$

(12)

The unknown DC voltage vectors  $\overline{\mathbf{V}}_{dq}^m$  on right hand side of (12) are replaced with filtered vectors  $\overline{\mathbf{V}}_{dq}^{m*}$ . Whereas, the unknown vectors  $\overline{\mathbf{V}}_{dq}^n$  on left hand side of (12) are replaced with estimated vectors  $\overline{\mathbf{V}}_{dq}^{n*}$ . The new form of (12) is given in (13), where  $\overline{\mathbf{V}}_{dq}^{m*}$  are obtained by passing the estimated  $\overline{\mathbf{V}}_{dq}^{m*}$  through a LPF using (14) to remove any residual oscillations from the decoupled voltage vectors. For optimally damped response, the cutoff frequency  $\omega_{cut}$  of the LPF<sub>1</sub> is selected as  $\omega/\sqrt{2}$  for positive component and  $\omega/4.5$  of the LPF<sub>2</sub> for DC component (with  $\omega$  being the nominal grid frequency). The LPFs is used to allow the proper subtraction of voltage vectors (and not to filter out the DC-offset); hence, the dynamic response of the PLL remains unaffected.

$$\begin{bmatrix} \overline{\mathbf{V}}_{dq}^{+1\prime} \\ \overline{\mathbf{V}}_{dq}^{0\prime} \end{bmatrix} = \begin{bmatrix} \mathbf{v}_{dq}^{+1} \\ \mathbf{v}_{dq}^{0} \end{bmatrix} - \begin{bmatrix} [0] & [T_{dq}^{+1-(0)}] \\ [T_{dq}^{0-(+1)}] & [0] \end{bmatrix} \begin{bmatrix} \overline{\mathbf{V}}_{dq}^{+1*} \\ \overline{\mathbf{V}}_{dq}^{0*} \end{bmatrix}$$

(13)

$$\overline{\mathbf{V}}_{dq}^{m*} = \frac{\omega_{cut}}{s + \omega_{cut}} \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \overline{\mathbf{V}}_{dq}^{m'} \tag{14}$$

To obtain oscillation free voltage vectors, (13) can be solved and rearranged, as expressed below:

$$\overline{\mathbf{V}}_{dq}^{n\prime} = \left[T_{dq}^{n}\right] \overline{\mathbf{V}}_{\alpha\beta}^{n\prime} = \left[T_{dq}^{n}\right] \left(\mathbf{v}_{\alpha\beta} - \sum_{m \neq n} \overline{\mathbf{V}}_{\alpha\beta}^{m*}\right) \tag{15}$$

where  $\overline{\mathbf{V}}_{\alpha\beta}^{m*} = [T_{dq}^{-m}]\overline{\mathbf{V}}_{dq}^{m*}$ .

The multiple use of (15) for +1 and 0 results in fundamental voltage vector in dq-frame  $\mathbf{V}_{dq}^{+1\prime}$ , which is free from the DC-offset, (see Fig. 2).

The harmonics/interharmonics are now compensated using the proposed HIH unit. Note that the proposed HIH is simple yet effective compensation method that does not require prior knowledge of individual harmonics/interharmonic to be compensated. Furthermore, unlike MHDCPLL the proposed technique does not need multiple transformations for the elimination of each individual harmonic, resulting in a simpler and computationally efficient harmonic mitigation, while maintaining the faster dynamic response of the PLL.

The DC-offset compensated positive voltage vector  $\overline{\mathbf{V}}_{dq}^{+1'}$  is transferred to the HIH unit for the effective compensation of contained harmonics and interharmonics. The first step involved in HIH is to pass  $\overline{\mathbf{V}}_{dq}^{+1'}$  (which is free from DC-offset but contains harmonics and interharmonics) through a High

Pass Filter (HPF) so that all the high frequency oscillations go through it and at the same time, it blocks the DC-term associated with +1 component. Thus, the output of HPF is a voltage vector,  $\overline{\mathbf{V}}_{dq}^{+1/HF}$ , that contains oscillations due to harmonics and interharmonics only, given in (16).

$$\overline{\mathbf{V}}_{dq}^{+1'HF} = [HPF]\overline{\mathbf{V}}_{dq}^{+1'} = \frac{s}{s + \omega_b} \overline{\mathbf{V}}_{dq}^{+1'}$$

(16)

The cutoff frequency  $\omega_h$ , considering the PLL's accuracy and faster dynamics, falls in a range  $0.2\omega < \omega_h < 0.5\omega$ . In the end, the  $\overline{V}_{dq}^{+1'HF}$  containing undesired oscillations is subtracted from the actual input  $\overline{V}_{dq}^{+1'}$  (containing  $dq^{+1}$ -DC-term and oscillations), enabling an effective decoupling of harmonics and interharmonics. This result in a clean fundamental voltage vector  $\overline{V}_{dq-pp}^{+1'}$ , which is free from DC-offset, harmonics and interharmonics, given in (17).

$$\overline{\mathbf{V}}_{dq-pp}^{+1'} = \overline{\mathbf{V}}_{dq}^{+1'} - \overline{\mathbf{V}}_{dq-HF}^{+1'} \\

= \overline{\mathbf{V}}_{dq'}^{+1'} - [HPF] \overline{\mathbf{V}}_{dq}^{+1'} \tag{17}$$

The q-component of the resulting  $\overline{\mathbf{V}}_{dq-pp}^{+1\prime}$  is passed to the PD part to extract the required phase  $(\theta'_g)$  and frequency  $(f'_g)$  of the grid voltage.

## 3. Frequency-Phase Decoupling and Integral Update (FPDIU) Phase Detector

The PD part of the proposed PLL is equipped with FPD method [15] to avoid unwanted frequency swings and oscillations that occurs in the event of grid voltage faults, phase variations and other grid disturbances. The FPD is achieved by taking out the term  $(\theta_{error}, k_p)$  from the frequency estimation loop of the PD, as expressed in (18). In addition, the frequency overshoot of the PLL under grid faults is adaptively controlled and reduced by applying a tuning mechanism to update the integral coefficient of the PI controller. The integral parameter  $T_i$  is updated by multiplying it with a factor  $(U_f)$  that depends on the fundamental vector  $\overline{\mathbf{V}}_{dq-pp}^{+1\prime}$  and the phase error  $\theta_{error}$ , as given in (19), where  $\lambda$  is the damping factor, holding value in a range of 50 to 100 [15]. Thus, the FPDIU results in lower frequency overshoot of the PLL and helps in reducing the oscillations/swings in the events of grid disturbances. Consequently, the lower overshoot of the proposed PLL can be interpreted as the improvement to the PLL's time response as it can be now tuned for even faster response without violating the assigned grid frequency limits.

$$f_g' = \frac{1}{2\pi} \left[ \theta_{error} \cdot \frac{1}{t_{is}} + \omega_{nom} \right]$$

(18)

$$U_f = \left(1 + \lambda \left(\theta_{error} / \sqrt{\left(\overline{v}_{d\text{-}pp}^{+1'}\right)^2 + \left(\overline{v}_{q\text{-}pp}^{+1'}\right)^2}\right)^2\right)$$

(19)

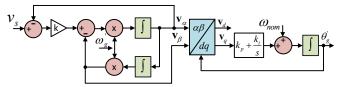

#### B. The Existing SOGI-PLL

In the implementation of SOGI-PLL, the vector  $v_s$  is converted into in-phase and quadrature component  $v_{s_{\alpha}}$  and  $v_{s_{\beta}}$  respectively, which are 90° apart, as shown in Fig. 3. The

transfer function of  $v_{s_{\alpha}}$  and  $v_{s_{\beta}}$  with respect to input voltage is given in (20) and (21).

$$H_{\alpha}(s) = \frac{v_{s_{\alpha}}(s)}{v_{s}(s)} = \frac{k\omega_{g}s}{s^{2} + k\omega_{g}s + \omega_{g}^{2}}$$

(20)

$$H_{\beta}(s) = \frac{v_{s_{\beta}}(s)}{v_{s}(s)} = \frac{k\omega_{g}^{2}}{s^{2} + k\omega_{g}s + \omega_{g}^{2}}$$

(21)

where,  $\omega_g$  is the estimated grid frequency and k is SOGI weighting factor.

The resulting in-quadrature  $v_{s_{\alpha\beta}}$  is transformed to rotating reference frame by using (10) followed by a PI controller based phase detector part.

Fig. 3: Schematic diagram of SOGI-PLL.

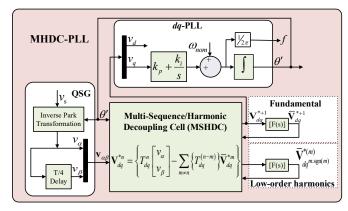

#### C. The Existing MHDC-PLL

The MHDC-PLL consists of two parts, QSG and MHDC. The QSG part is composed of quarter delay transformation and IPT technique. The vector  $v_s$  is passed through IPT, further to which quarter delay technique is used to extract in-quadrature components  $v_{s_{\alpha\beta}}$  as shown in Fig. 4, providing some attenuation to higher order harmonics.

Fig. 4: Schematic diagram of MHDC-PLL

The low order harmonics are removed from in-quadrature component using the MHDC part by selective harmonic elimination. Further, the vector  $v_{s_{\alpha\beta}}$  is transformed to dq-reference frame, where phase angle is extracted by forcing the q-component to zero by using a PI controller. For the sake of fair comparison, SOGI and MHDC PLL are tuned in a same way as of the proposed PLL.

#### III. TUNING PROCEDURE OF THE PROPOSED PLL

For the accurate estimation and response of the PLL, the optimal tuning is very important and critical. The small signal linearized model of the PLL is used for the calculation of

tuning parameters,  $k_p$  and  $T_i$ . The closed loop Transfer Function (TF) of the proposed PLL (based on small signal analysis) is given in (22).

$$TF_{\theta} = \frac{\theta_g'}{\theta} = \frac{2\zeta \omega_n \cdot s + \omega_n^2}{s^2 + 2\zeta \omega_n \cdot s + \omega_n^2} = \frac{k_p \cdot s + \frac{1}{T_i}}{s^2 + k_p \cdot s + \frac{1}{T_i}}$$

(22)

Where,  $\theta$  is the actual grid voltage phase angle and  $\theta_a$  is the estimated angle of the PLL. The system in (22) presents a typical second-order transfer function and can be tuned based on natural frequency  $\omega_n$  and damping coefficient  $\zeta$ . By setting the value of  $\zeta$  to 1.414 (for optimal damping) and expressing  $\omega_n$  in terms of settling time (ST), the tuning parameters  $k_p$  and  $T_i$  are given in (23). The Settling time (ST) is set 100 ms for the for all PLLs considered for benchmarking including the proposed, and the values of  $k_p$  and  $T_i$  are calculated as 92 and 4256, respectively.

$$k_p = \frac{9.2}{ST}$$

and  $T_i = (0.047 \cdot \zeta^2 \cdot ST^2)$  (23)

The proposed PLL is further equipped with integral update in order to control the the frequency overshoot of the PLL under grid faults, where  $T_i$  is adaptively adjusted based on grid voltage,  $\theta_{error}$  and damping factor  $\lambda$ . The integral update is applied by multiplying pre-calculated integral coefficient (23) with an adaptive factor  $U_f$  given in (19) and thus, the revised  $T_i$  considering integral update is shown in (24).

$$T_i = (0.047 \cdot \zeta^2 \cdot ST^2) U_f \tag{24}$$

Thus, for the proposed PLL,  $k_p$  is constant for given settling time but the value of  $T_i$  is adaptively updated considering the voltage and  $\theta_{error}$ , hence it adjust itself according to the grid variation. Moreover, the ST can be varied according to the required dynamics. It is worth mentioning here that parameters of MHDCPLL and SOGIPLL are also tuned for 100 ms for the sake of fair comparison.

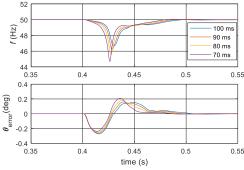

Fig. 5: Response of proposed PLL for different settling time.

Table 1: Tuning parameter of proposed PLL for different settling time.

| Settling Time (ms) | $k_p$   | $T_i$ |

|--------------------|---------|-------|

| 100                | 92      | 4256  |

| 90                 | 102.2   | 5255  |

| 80                 | 115     | 6651  |

| 70                 | 131.428 | 8687  |

The effect of parameter setting on the performance of proposed PLL for different settling time under -25° phase variation is shown in Fig. 5. The set of tuning parameters for various settling times (calculated using (23)) is given in Table 1 and the corresponding variations in the estimated frequency and error are presented in Fig. 5, where with normal initial grid voltage a -25° phase change occurs at 0.4 s.

#### IV. BODE ANALYSIS AND COMPUTATIONAL COMPLEXITY

The DHIH transfer function is the combination of transfer characteristics from the DC-offset block and the HIH unit. For DC block,  $\overline{\mathbf{V}}_{\alpha\beta}^{n\prime}$  is extracted from (15) and rewritten as:

$$\overline{\mathbf{V}}_{\alpha\beta}^{n\prime} = \mathbf{v}_{\alpha\beta} - \sum_{m \neq n} \overline{\mathbf{V}}_{\alpha\beta}^{m*} \tag{25}$$

Substituting (26) in (25), results in (27).

$$\bar{\mathbf{V}}_{\alpha\beta}^{m*} = \begin{bmatrix} T_{dq}^{-m} \end{bmatrix} \bar{\mathbf{V}}_{dq}^{m*} = \begin{bmatrix} T_{dq}^{-m} \end{bmatrix} [LPF] \bar{\mathbf{V}}_{dq}^{m\nu} \\

= \begin{bmatrix} T_{dq}^{-m} \end{bmatrix} [LPF] \begin{bmatrix} T_{dq}^{m} \end{bmatrix} \bar{\mathbf{V}}_{\alpha\beta}^{m\nu} \\

\bar{\mathbf{V}}_{\alpha\beta}^{n\nu} = \mathbf{v}_{\alpha\beta} - \sum_{m \neq n} (\begin{bmatrix} T_{dq}^{-m} \end{bmatrix} [LPF] \begin{bmatrix} T_{dq}^{m} \end{bmatrix} \bar{\mathbf{V}}_{\alpha\beta}^{m\nu} )$$

(26)

$$\overline{\mathbf{V}}_{\alpha\beta}^{n\prime} = \mathbf{v}_{\alpha\beta} - \sum_{m \neq n} ([T_{dq}^{-m}][LPF][T_{dq}^{m}]\overline{\mathbf{V}}_{\alpha\beta}^{m\prime})$$

(27)

Finally, expanding (27) for the fundamental component, that is for n = +1:

$$\overline{\mathbf{V}}_{\alpha\beta}^{+1\prime} = \mathbf{v}_{\alpha\beta} - [T_{dq}^{0}][LPF][T_{dq}^{0}]\overline{\mathbf{V}}_{\alpha\beta}^{0\prime}$$

(28)

In order to obtain the transfer function  $\bar{\mathbf{V}}_{\alpha\beta}^{+1*}/\mathbf{v}_{\alpha\beta}$  of DCoffset block, (28) is substituted with  $\overline{\mathbf{V}}_{\alpha\beta}^{0\prime}$  (using n=0 in (27)) and the resultant is given as follows:

$$\overline{\mathbf{V}}_{\alpha\beta}^{+1'} = \mathbf{v}_{\alpha\beta} - [T_{dq}^{0}][LPF][T_{dq}^{0}]\mathbf{v}_{\alpha\beta} + ([T_{dq}^{-0}][LPF][T_{dq}^{0}])([T_{dq}^{-1}][LPF][T_{dq}^{+1}])\overline{\mathbf{V}}_{\alpha\beta}^{+1'}$$

(29)

The final transfer function for DC-offset is achieved below by rearranging (29) as:

$$TF_{DC} = \frac{\overline{\mathbf{V}}_{\alpha\beta}^{+1'}}{\mathbf{v}_{\alpha\beta}}$$

$$= \frac{1 - ([T_{dq}^{0}][LPF][T_{dq}^{0}])}{1 - ([T_{dq}^{0}][LPF][T_{dq}^{0}])([T_{dq}^{-1}][LPF][T_{dq}^{+1}])}$$

(30)

The transfer function for  $[T_{dq}^{-x}][LPF][T_{dq}^{x}]$  is calculated using Euler formula in complex domain, as expressed in (31), where  $\omega_{cut}$  is LPF's cutoff frequency for  $x^{th}$  frequency component.

$$[T_{dq}^{-x}][LPF][T_{dq}^{x}] = \frac{\omega_{cut}}{s + (\omega_{cut} - j \cdot x \cdot \omega)}$$

(31)

The HIH unit transfer function on the other hand is obtained by multiplying  $T_{da}^{-1}$  with (17), given as (32).

$$\begin{bmatrix} T_{dq}^{-1} \end{bmatrix} \overline{\mathbf{V}}_{dq-pp}^{+1'} = \begin{bmatrix} T_{dq}^{-1} \end{bmatrix} \overline{\mathbf{V}}_{dq}^{+1'} - \begin{bmatrix} T_{dq}^{-1} \end{bmatrix} [HPF] \overline{\mathbf{V}}_{dq}^{+1'} \\ \overline{\mathbf{V}}_{\alpha\beta-pp}^{+1'} = \overline{\mathbf{V}}_{\alpha\beta}^{+1'} - \begin{bmatrix} T_{dq}^{-1} \end{bmatrix} [HPF] [T_{dq}^{+1}] \overline{\mathbf{V}}_{\alpha\beta}^{+1'} \end{bmatrix} \tag{32}$$

where,

$$\overline{\mathbf{V}}_{\alpha\beta}^{+1\prime} = [T_{da}^{-1}]\overline{\mathbf{V}}_{da}^{+1\prime}$$

Therefore, rearranging (32) results in HIH module transfer function as:

$$TF_{HIH} = \frac{\overline{\mathbf{V}}_{\alpha\beta-pp}^{+1'}}{\overline{\mathbf{V}}_{\alpha\beta}^{+1'}} = 1 - [T_{dq}^{-1}][HPF][T_{dq}^{+1}]$$

(33)

Hence, the complete transfer function for the overall DHIH module is obtained by multiplying (30) and (33), and is given as:

$$TF_{DHIH} = TF_{DC}TF_{HIH} = \left(\frac{\overline{\mathbf{V}}_{\alpha\beta}^{+1'}}{\mathbf{v}_{\alpha\beta}}\right) \left(\frac{\overline{\mathbf{V}}_{\alpha\beta-pp}^{+1'}}{\overline{\mathbf{V}}_{\alpha\beta}^{+1'}}\right)$$

$$= \left(\frac{1 - ([T_{dq}^{0}][LPF][T_{dq}^{0}])}{1 - ([T_{dq}^{0}][LPF][T_{dq}^{-1}][LPF][T_{dq}^{+1}])}\right) (1^{(34)}$$

$$- [T_{dq}^{-1}][HPF][T_{dq}^{+1}])$$

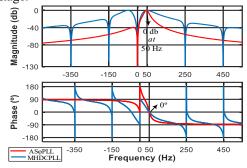

The Bode diagram in Fig. 6 compares the proposed PLL with MHDCPLL. The proposed ASφPLL passes the positive sequence component (50 Hz) with unity gain and zero phase shift. The DC-component (0 Hz) and all other harmonics/interharmonics are blocked by large negative gains and phase shifts. The MHDCPLL has limited filtering capabilities for interharmonics and works only for selected low-order harmonics. The maximum filtering capability of the MHDCPLL for the harmonics other than the selected, as seen from the Bode is −39 db, whereas for the proposed PLL, the maximum filtering capability is around −75.5 db. This shows, the proposed PLL has better suppression capability and is able to compensate for all harmonics/interharmonics present in the grid voltage.

Fig. 6: Bode analysis of the proposed PLL

Table 2: Complexity and performance comparison of four PLLs.

| P                           | LLs             | ASφPLL              | MHDCPLL            | SOGIPLL           | NMAFPLL            |

|-----------------------------|-----------------|---------------------|--------------------|-------------------|--------------------|

| Mathematical operations     |                 | × = 43              | × = 342            | × = 13            | × = 47             |

|                             |                 | + = 12              | +=69               | +=7               | += 12              |

|                             |                 | - = 8               | - = 135            | - = 3             | - = 7              |

| Processing time             |                 | 20.1 μs<br>(12.85%) | 156.4 μs<br>(100%) | 6.2 μs<br>(3.96%) | 21.6 μs<br>(13.8%) |

| -                           | Harmonics       | <b>√</b>            | <b>✓</b>           | ×                 | <b>✓</b>           |

| Features                    | Inter-          | ✓                   | ×                  | ×                 | ✓                  |

| (Accurate estimation under) | Dc-offset       | <b>√</b>            | ✓                  | ×                 | ✓                  |

|                             | Freq. variation | <b>√</b>            | ✓                  | ✓                 | ✓                  |

|                             | Phase           | <b>√</b>            | ✓                  | ✓                 | ✓                  |

| Sag                         |                 | ✓                   | ✓                  | ✓                 | ✓                  |

The complexity analysis provided in Table 2 for the four PLLs proves that the proposed PLL has significantly less

complexity than MHDCPLL and NMAFPLL and work for all the abnormal grid conditions. The SOGIPLL on the other hand, is less complex than proposed PLL however it does not work for the harmonics, interharmonics and DC-offset. The algebraic operators (additions, subtractions multiplications) required by each PLL are counted and in addition, all PLLs are implemented using Texas Instrument TMS320F28335 microcontroller and their processing times are experimentally measured. The proposed PLL eliminates all the faults and requires a smaller number of algebraic operators and less processing time compared to the other PLLs. This validates the lower complexity and robust performance of the ASφPLL.

For real-time applications, the control algorithm is always implemented in the embedded microcontroller (with limited processing resources). Consequently, for complex algorithms, embedded microcontrollers are unable to operate at required sampling rate and a reduction in sampling rate is required which increases the discretization error. Less complex algorithms are appropriate solution to this problem and, accordingly the proposed PLL is a suitable candidate for such applications. The lower computational complexity of the proposed PLL is a very important benefit and characteristic for the grid side converter control. It ensures that the sampling rate of the PLL will not be compromised in order to accommodate the new features, thus, the applicability of the proposed technique on commercial inverters is not limited by the computational resources of the embedded DSP/microcontroller.

#### V. VALIDATION OF THE PROPOSED PLL

### A. Simulation Results

This section validates the accurate estimation of proposed PLL and compares it with MHDCPLL and SOGIPLL. The sampling frequency used is 10 kHz.

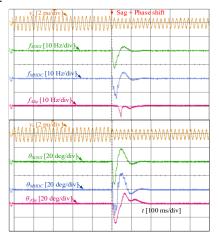

The first case analyses the behavior of PLLs under gird voltage harmonics, phase change and frequency variation, Fig. 7. With normal initial grid voltage, 4% 3<sup>rd</sup> and 4.5% 5<sup>th</sup> harmonics are injected at 0.3 s. The SOGIPLL suffers from oscillations, as it is not immune to harmonics. The proposed ASφPLL provides faster compensation, whereas the MHDCPLL takes 16 ms to fully compensate the harmonics. Following this, a phase change of -28° occurs at 0.4 s, to which MHDCPLL and SOGIPLL suffer from a very high frequency overshoot (of around -7.5 Hz). At 0.6 s a frequency change event of -2 Hz occurs, to which the MHDCPLL suffers from oscillations. However, the ASφPLL results in an accurate and oscillation free estimation of frequency and phase angle.

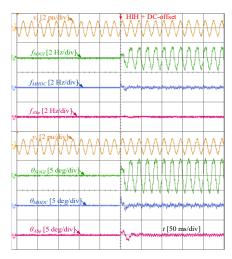

The second case analyses the PLLs under interharmonics (5.3% 2.8<sup>th</sup> and 4.1% 7.2<sup>th</sup>), DC-offset plus the harmonic (4% DC-offset and 5% 7<sup>th</sup> harmonic) and voltage sag (25%), depicted in Fig. 8. The voltage is distorted with interharmonics at 0.3 s. The MHDCPLL and SOGIPLL suffers from oscillations, with no immunity to interharmonics. The

suppression provided by MHDC to  $2.8^{th}$  interharmonic is around -16 dB whereas the proposed PLL provides an attenuation of -41.06 dB. Both MHDC and AS $\phi$  PLLs survive the DC-offset and harmonic event at 0.4 s, however, the estimated quantities by SOGI suffer from oscillations. Following this, voltage sag occurs at 0.5 s and reverts back to normal at 0.65 s, to which the proposed PLL results in lower frequency overshoot.

Fig. 7: Performance comparison of three PLLs under first case.

Fig. 8: Performance comparison of three PLLs under second case.

Table 3: Summary of result presented in Fig. 7 and Fig. 8.

|                   |           |                            | Fig. 7 |       | Fig. 8  |    |      |      |

|-------------------|-----------|----------------------------|--------|-------|---------|----|------|------|

| Fault types       |           |                            | Phase  |       |         |    | 2    |      |

| PLL'              | s types   |                            | Harm.  | +     | Phase + | IH | H+DC | Sag  |

|                   |           |                            |        | Harm  | Harm    |    |      |      |

|                   | Overshoot | Frequency (Hz)             | -      | 7.5   | 2.27    | -  | -    | -    |

| 면<br>다            | Overshoot | $\theta_{ m error}$ (deg)  | -      | 22.42 | 5.9     | -  | -    | -    |

| SOGI<br>PLL       | Settling  | Frequency (ms)             | -      | 90    | 80      | •  | -    | -    |

|                   | time      | $\theta_{\rm error}$ (ms)  | -      | 80    | 69      | •  | -    | -    |

| MHDC<br>PLL       | Overshoot | Frequency (Hz)             | -      | 7.5   | 2.2     | -  | 0.48 | 1.8  |

|                   |           | $\theta_{\rm error}$ (deg) | -      | 22.41 | 5.08    | -  | 1.04 | 6.61 |

| 鱼鱼                | Settling  | Frequency (ms)             | -      | 90    | 80      | 1  | 50   | 85   |

| ~                 | time      | $\theta_{\rm error}$ (ms)  | -      | 80    | 80      | ı  | 47   | 87   |

|                   | Overahaat | Frequency (Hz)             | -      | 3.73  | 2.14    | ı  | 0.12 | 0.14 |

| $_{PLL}^{AS\phi}$ | Overshoot | $\theta_{ m error}$ (deg)  | -      | 17.53 | 5.08    | -  | 1.84 | 2.27 |

|                   | Settling  | Frequency (ms)             | -      | 90    | 60      | -  | 29   | 54   |

|                   | time      | $\theta_{\rm error}$ (ms)  | -      | 80    | 69      | -  | 47   | 87   |

The results presented in Fig. 7 and Fig. 8 are tabulated and summarized in Table 3. For the harmonics and interharmonics, only oscillations are present without over/undershoot. The performance and estimation accuracy of proposed technique is also compared with a recent Nonadaptive Moving Average Filter based Phase Locked Loop (NMAFPLL) [26] in addition to SOGIPLL and MHDCPLL under a set of abnormal grid conditions.

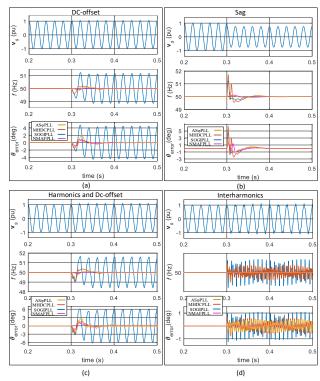

Fig. 9: Performance comparison of four PLLs under abnormal grid conditions

All the four PLLs (AS\(\phi\)PLL, SOGIPLL, MHDCPLL and NMAFPLL) are further subjected to certain set of conditions. First of all, a DC-offset of 4% (that is 13 V) with respect to the fundamental voltage is introduced in Fig. 9 (a). The SOGIPLL suffers from high oscillations in both frequency and phase estimation. However, on other side, the remaining three including proposed PLL removes DC-offset accurately with less overshoot and settling time. Similarly, the performance of four PLLs to 25% sag (325V to 244V) is shown in Fig. 9 (b). The MHDC- and SOGI- PLLs suffer from high overshoot and settling time in the estimation of both  $\theta_{error}$  and frequency. The NMAFPLL removes the effect of voltage sag but it has slightly more settling time in comparison to ASφPLL. The proposed PLL performs well for the frequency and phase error estimation. Furthermore, all the PLLs are subjected to 4% of 5<sup>th</sup> harmonic and 5.3% of DC-offset occurring simultaneously, Fig. 9 (c). The SOGIPLL suffers from high oscillation in both estimations in comparison with the other PLLs, as can be seen from Fig. 9 (c). The 4% of 5.2th and 5.3% of 7.2th interharmonics are induced at 0.3 s in Fig. 9 (d). Less than 0.5° oscillations are observed in NMAFPLL and the proposed PLL.

For the frequency estimation, the proposed and NMAFPLL has zero overshoot and settling time, in comparison with the MHDCPLL and SOGIPLL. Thus, the proposed PLL presents better performance for abnormal grid conditions but with lower complexity. The results presented in Fig. 9 are summarized in the Table 4.

| Fault types PLL's types |            |                            | DC-offset | Sag  | HIH +<br>DC-offset | IH    |

|-------------------------|------------|----------------------------|-----------|------|--------------------|-------|

|                         | Overshoot  | Frequency (Hz)             | 1.25*     | 1.24 | 1.64*              | 0.3*  |

| SOGI                    | Overshoot  | θ error (deg)              | 4.77*     | 4.47 | 6.09*              | 1.23* |

| S =                     | Settling   | Frequency (ms)             | -         | 93   | -                  | -     |

|                         | time       | $\theta_{\rm error}$ (ms)  | -         | 85.5 | -                  | -     |

| 7.)                     | Overshoot  | Frequency (Hz)             | 0.4       | 1.74 | 1.14               | 0.19* |

| MHDC                    | Oversnoot  | $\theta_{\rm error}$ (deg) | 1.34      | 6.39 | 2.75               | 0.7   |

|                         | Settling   | Frequency (ms)             | 74        | 100  | 74                 | -     |

|                         | time       | $\theta_{\rm error}$ (ms)  | 41        | 90   | 75                 | -     |

|                         | Overshoot  | Frequency (Hz)             | 0.15      | 0.12 | 0.19               | -     |

| ASQ<br>PLL              |            | $\theta_{\rm error}$ (deg) | 2         | 1.9  | 2.8                | 0.32* |

| A I                     | Settling   | Frequency (ms)             | 44        | 64   | 54                 | -     |

|                         | time       | $\theta_{\rm error}$ (ms)  | 72        | 43   | 70                 | -     |

| NMAF<br>PLL             | Overaghant | Frequency (Hz)             | 0.14      | 0.13 | 0.12               | -     |

|                         | Overshoot  | $\theta_{\rm error}$ (deg) | 0.94      | 1.9  | 1.33               | 0.22* |

|                         | Settling   | Frequency (ms)             | 44        | 86   | 54                 | -     |

| -                       | time       | $\theta_{\rm error}$ (ms)  | 72        | 55.6 | 65.7               | -     |

<sup>\*</sup> Recurrent oscillations

#### B. Experimental Results

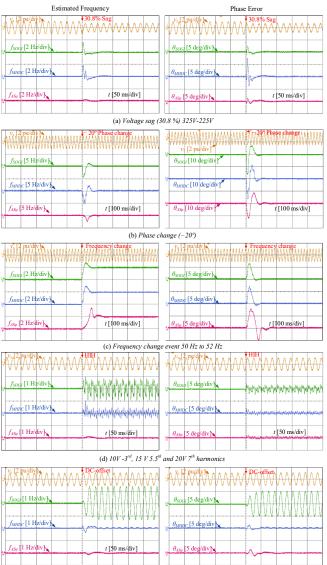

This section is to experimentally validate the proposed AS $\phi$ PLL and compare its performance with the state-of-the-art MHDCPLL and SOGIPLL. We use the dSPACE real-time simulator MicroLabBox and DS1202 DSP board to achieve our results. The experimental validation is carried out under various set of grid conditions, divided in to three case studies where: 1) the results of existing and proposed techniques are presented for all fault types individually, 2) the results are provided for two faults occurring at the same time, and 3) the results are provided for a set of 3 fault conditions. The sampling frequency of 10 kHz is used in the experimental results.

Case 1: This case involves experimental validation of PLLs under various set of grid conditions including frequency variation, voltage sag, phase change, voltage harmonics, interharmonics and DC-offset, as shown in Fig. 7. In all the experimental results, a red arrow is used to mark the point of disturbance and is labelled with the respective grid scenario.

The experimental results in Fig. 10 (a) investigates the response of MHDCPLL (blue color), SOGIPLL (green color) and proposed PLL (pink color) to a voltage sag event of 30.8%. The grid voltage is initially at 1 pu, which however, is varied to 0.692 pu at the point marked with red arrow. The proposed PLL responds to this voltage sag event and accurately tracks the desired grid phase and frequency. The faster dynamics of PLL can be seen from the settling time of both phase (52 ms) and frequency (23 ms). In addition, the peak value of  $\theta_{error}$  and frequency (1.35° and 0.2 Hz respectively) validates the accurate response of the proposed AS $\varphi$ PLL. On the other hand,

the frequency overshoot of SOGIPLL and MHDCPLL is 1.6 Hz, 1.95 Hz and settling time is 55 ms, 50 ms, respectively, as shown in Fig. 10 (a). Likewise, the overshoot of SOGIPLL for phase error is 2.75° with 50 ms settling time and for MHDCPLL is 7.6° and settled in 75 ms.

Fig. 10: Experimental validation of the proposed AS $\phi$ PLL and its comparison with MHDCPLL and SOGIPLL under, (a) 30.8% voltage sag, (b) -20° phase change, (c) 50 to 52Hz frequency change, (d) harmonics and interharmonics, and (e) 15V DC-offset.

(e) 15V DC offset

Furthermore, the performance of PLLs are analyzed under a phase change event. With zero initial phase, the grid voltage is subjected to a phase change of  $-20^{\circ}$  and the corresponding results are depicted in Fig. 10 (b). The overshoot of SOGIPLL for frequency estimation is 4.5 Hz with a settling time of 75 ms. The  $\theta_{error}$  experiences an overshoot of 16.3° and get settled in 100 ms. The MHDCPLL gives an overshoot of 5.2 Hz and 16.7° for frequency and  $\theta_{error}$  with the settling time of 85 ms and 100 ms, respectively. The AS $\varphi$ PLL is also capable of mitigating the phase changes, and thus, reverts the estimated

phase and frequency to their desired values immediately after the phase fault occurs. The overshoot in phase error and frequency are respectively equal to  $12^{\circ}$  and 2.7 Hz, whereas the response time is approximately 100 ms and 62 ms for  $\theta_{error}$  and estimated frequency. Thus, verifying the fast and accurate response of the proposed PLL to a phase change.

The response of three PLLs to a frequency variation of 2 Hz is shown in Fig. 10 (c). With initial frequency of 50 Hz, it is varied to 52 Hz at the point marked. As seen, the proposed AS $\phi$ PLL accurately tracks the change in frequency with a response time of 120 ms and the overshoot of 1.4 Hz. Similarly, the response time of SOGI and MHDCPLL is 60 ms and 100 ms, with the overshoot of 0.95 Hz and 1 Hz, respectively. The error require approximately 150 ms to settle back to zero and the overshoot is 8° for the proposed PLL, 100 ms with an overshoot of 6.9° for SOGIPLL and 100 ms with 7.2° overshoot for MHDCPLL.

In Fig. 10 (d), the PLLs are further investigated for grid voltage harmonic and interharmonic distortion. With normal initial conditions, the grid voltage is distorted with 3% of 3<sup>rd</sup> harmonic, 4.6% of 5.5th interharmonic, and 6.1% of 7th harmonic. The percentage of harmonics and interharmonics are calculated with respect to the fundamental component. Compared to the proposed PLL, high oscillations are observed in the estimated quantities for both SOGIPLL and MHDCPLL. The overshoot in the frequency and phase error are respectively observed as 1 Hz and 2° for both SOGI and MHDCPLL, followed by large repeating oscillations. The distortion in the grid voltage with faster dynamic response and results in oscillation-free frequency and low  $\theta_{error}$  oscillations in comparison with other PLLs. The peak value of oscillations observed in the phase and frequency of proposed PLL is respectively equal to 1° and 0.18 Hz, This shows very low magnitudes and the better performance of the proposed ASφPLL in comparison to the existing methods.

Table 5: Summary of results presented in Fig. 10.

|                |           | Fault types                | Voltage | Phase  | Frequency | нін  | DC-    |

|----------------|-----------|----------------------------|---------|--------|-----------|------|--------|

| PLL's types    |           |                            | sag     | change | change    | шп   | offset |

|                | Overshoot | Frequency (Hz)             | 1.6     | 4.5    | 0.95      | 1    | 1.5    |

| Ę Ţ            |           | $\theta_{\rm error}$ (deg) | 2.75    | 16.3   | 6.9       | 2    | 5      |

| Settling       |           | Frequency (ms)             | 55      | 75     | 60        | ı    | -      |

|                | time      | $\theta_{\rm error}$ (ms)  | 50      | 100    | 100       | ı    | -      |

| MHDC<br>PLL    | Overshoot | Frequency (Hz)             | 1.95    | 5.2    | 1         | 1    | 0.4    |

|                |           | $\theta_{\rm error}$ (deg) | 7.6     | 16.7   | 7.2       | 2    | 1.5    |

|                | Settling  | Frequency (ms)             | 50      | 85     | 100       | -    | 48     |

|                | time      | $\theta_{\rm error}$ (ms)  | 75      | 100    | 100       | ı    | 60     |

| AS\$\text{PLL} | Overshoot | Frequency (Hz)             | 0.2     | 2.7    | 1.4       | 0.18 | 0.16   |

|                |           | $\theta_{\rm error}$ (deg) | 1.35    | 12     | 8         | 1    | 1.5    |

|                | Settling  | Frequency (ms)             | 23      | 62     | 120       | -    | 40     |

|                | time      | $\theta_{\rm error}$ (ms)  | 52      | 100    | 150       | -    | 60     |

Finally, the PLLs are analyzed and examined for the case of DC-offset in the grid voltage, and the response of all PLLs to this disturbance is shown in Fig. 10 (e). The grid voltage is shifted in magnitude by injecting a DC-offset of 4.6% (15 V) of peak grid voltage (i.e. 325.27). The proposed PLL

accurately respond to DC-offset and remove the effect of fundamental frequency oscillation via mathematical cancellation DC-offset cell and results in accurate and oscillation-free estimation of phase/frequency, however, the MHDCPLL suffers from low and SOGI from high oscillations. The peak value of frequency oscillations at the point of fault is 0.16 Hz, 0.4 Hz and 1.5 Hz respectively for AS $\phi$ PLL, MHDCPLL and SOGIPLL. Likewise, the peak value of phase error is 1.5°, 1.5° and 5°, respectively. This verifies the outstanding performance of the proposed AS $\phi$ PLL. The results of case 1 presented in Fig. 10 is summarized in Table 5.

Case 2: This case investigates the performance of proposed and existing techniques for a set of 2 faults (occurring simultaneously), given in Fig. 11 and Fig. 12.

The results in Fig. 11 show PLL responses for a voltage sag of 30.8% (1 p.u. to 0.692 p.u.) together with a phase change of  $-20^{\circ}$ . The red arrow indicates the point where both faults are induced. The proposed PLL suffers from low overshoot (8 Hz) and presents less settling time (125 ms) in the estimated frequency as compared to the MHDCPLL and SOGIPLL, whose overshoot is 15 Hz and 13 Hz, respectively and both settles in 150 ms. On the other hand, the overshoot of  $\theta_{error}$  for AS $\phi$ PLL, MHDCPLL and SOGIPLL is 28.5°, 38° and 33°, whereas, the settling time of 180 ms, 180 ms and 140 ms respectively as shown in Fig. 11. The results show the better performance of proposed technique with low overshoot for both frequency and phase error, and faster frequency estimation.

Fig. 11: Experimental validation of the proposed AS $\phi$ PLL and its comparison with MHDCPLL and SOGIPLL under 30.8% sag and  $-20^{\circ}$  phase change.

The second scenario investigate the effect of two simultaneous faults includes HIH and DC-offset, as shown in Fig. 12. The grid voltage is distorted with 3% of 7<sup>th</sup> harmonic, 4.6% of 5<sup>th</sup> harmonic, and 6.1% of 7.5<sup>th</sup> interharmonic along with a DC-offset of 4.6%. The proposed PLL accurately respond for this set of conditions and results in oscillation-free, fast and an accurate estimation of frequency and phase angle when compared to the other state of art techniques. The SOGIPLL suffers from high oscillation, and MHDCPLL also presents small oscillations, as shown in Fig. 12.

Fig. 12: Experimental validation of the proposed ASφPLL and its comparison with MHDCPLL and SOGIPLL under HIH, and DC-offset.

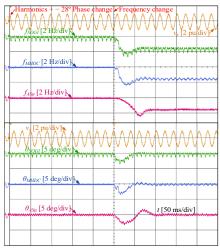

Fig. 13: Experimental validation of the proposed AS $\phi$ PLL and its comparison with MHDCPLL and SOGIPLL under harmonics,  $-28^{\circ}$  phase change and -1.5 Hz frequency variation.

Case 3: This case shows the performance of PLLs under three set of fault conditions (similar to the simulation results shown in Fig. 7). The three conditions are harmonics, phase change and frequency variation. A 3% of 3<sup>rd</sup> harmonics (10V) and 4.6 % of 5th harmonic (15V) along with the phase shift of -28° are already present in the voltage even before the starting point of the result, Fig. 13. A frequency variation of -2.5 Hz (that is 50 Hz to 48.5 Hz) is then introduced at the centre of waveform (marked with arrow) and performance of proposed and existing PLLs is compared. From the estimated frequency waveform shown in Fig. 13, it can be seen that the overshoot of ASφPLL, MHDCPLL and SOGIPLL is 0.8 Hz, 0.8 Hz and 1.15 Hz with the settling time of 87.5 ms, 92 ms and 100 ms respectively. Where both MHDC and SOGI PLLs suffer from unwanted oscillations in comparison with the proposed technique. The estimated frequency in the proposed technique does not suffer from undesired oscillations and swings because of the FPD added in the phase detector part of PLL. Furthermore, the overshoot of  $\theta_{error}$  for proposed PLL is 3.3°

against 3.5° for the other techniques with oscillations. All the results presented in Fig. 11, Fig. 12 and Fig. 13 are summarized in Table 6.

Table 6: Summary of results presented in Fig. 11, Fig. 12 and Fig. 13.

|                         |           |                           | Fig. 11           | Fig. 12                | Fig. 13 |

|-------------------------|-----------|---------------------------|-------------------|------------------------|---------|

| Fault types PLL's types |           | Sag+Phase                 | HIH+DC-<br>offset | H +<br>Phase +<br>freq |         |

|                         | Overshoot | Frequency (Hz)            | 13                | 1                      | 1.15    |

| SOGI                    | Overshoot | $\theta_{ m error}$ (deg) | 33                | -                      | 3.5     |

| SO                      | Settling  | Frequency (ms)            | 150               | ı                      | 100     |

|                         | time      | $\theta_{\rm error}$ (ms) | 140               | ı                      | 50      |

| 7.)                     | Overshoot | Frequency (Hz)            | 15                | 0.6                    | 0.8     |

| T                       |           | $\theta_{ m error}$ (deg) | 38                | 3                      | 3.5     |

| MHDC<br>PLL             | Settling  | Frequency (ms)            | 150               | 20                     | 92      |

| _                       | time      | $\theta_{\rm error}$ (ms) | 180               | 19                     | 50      |

|                         | Overshoot | Frequency (Hz)            | 8                 | 0                      | 0.8     |

| AS\$                    |           | $\theta_{ m error}$ (deg) | 28.5              | 2                      | 3.3     |

| A.<br>PI                | Settling  | Frequency (ms)            | 125               | 0                      | 87.5    |

|                         | time      | $\theta_{\rm error}$ (ms) | 180               | 25                     | 95      |

The proposed technique, in general, presents fast and accurate estimation with lower overshoot and almost no oscillations for various type of individual as well as combination of faults. Thus, the experimental results validate the accurate performance of proposed PLL towards synchronization of grid connected systems (V2G) under abnormal grid conditions.

### VI. IMPACT OF ACCURATE SYNCHRONIZATION ON GRID CONNECTED ESS

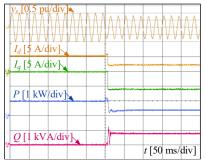

The performance of proposed PLL in estimating grid frequency and phase angle has been validated for several grid disturbances and as mentioned, synchronization directly affects the overall operation of grid connected ESS since it plays a vital role in transforming the voltages/currents to different domains, necessary for control purposes. Thus, it would be interesting to investigate the performance of proposed PLL for the case when it is used in the GSC controller (shown in Fig. 1) and compare it with the existing MHDCPLL. The PQ controller is designed in the synchronous reference frame based on the open-loop controller design. Thus, the reference currents  $(i_{dq}^{+1*})$  are generated based on P\*,  $Q^*$  and  $\overline{V}_{dq\cdot pp}^{+1\prime}$ , where,  $P^*$  and  $Q^*$  are the reference powers and  $\overline{V}_{dq-pp}^{+1\prime}$  is the fundamental oscillation-free voltage vector estimated by the PLL algorithm. The current controller is also designed in the synchronous reference frame and since, the investigation is carried out under distorted grid conditions, the current controller is enhanced with harmonic interhamronic compensation. Furthermore, a fault ride through scheme is integrated in to the PQ controller to provide appropriate voltage and frequency support in the event of grid faults. The FRT scheme provides a Q/P ratio of 2:1 under faults and helps in limiting the converter currents to ensure the safety of converter.

The quality of power flowing to/from the grid and the Total Harmonic Distortion (THD) of the injected current becomes important while investigating the operation of grid connected system. A test case is performed, where, the grid voltage is subjected to various disturbances and the effect of existing MHDCPLL and proposed  $AS\phi PLL$  on the overall operation of grid connected ESS is analyzed. The following three disturbances occur in the grid voltage:

- Harmonic and interharmonic (H+IH) condition: where grid voltage is distorted with 5th harmonic and 7.2th interharmonic each having 5% magnitude with respect to fundamental.

- 2. Interharmonic (IH) condition: where gird voltage has two interharmonics, 3.3<sup>th</sup> and 7.2<sup>th</sup> with 5% magnitude each.

- 3. Interharmonic and voltage sag: where a 20% voltage sag occurs under IH condition.

Fig. 14: Simulation results showing the effectiveness of accurate synchronization under distorted and faulty grid conditions. Note: The operation of RESS controller is based on MHDCPLL until 0.8~s and proposed  $AS\phiPLL$  is activated after 0.8~s.

The operation of grid-connected systems is depicted in Fig. 14 using the grid voltage vs, the dq-transformed fundamental currents  $\mathbf{i}_{dq}$ , the desired active/reactive power and the THD of injected current. From 0.3 s to 0.8 s, the MHDCPLL is in operation, whereas the proposed AS $\varphi$ PLL is activated for the rest of time. Clearly, under all the disturbances, the proposed PLL performs more accurately and enable the injection of high quality power and current. In contrast, the MHDCPLL, under voltage interharmonics, results in oscillations on the transformed currents, and in the active/reactive powers. Furthermore, the improved performance of the proposed PLL is clear from the THD of current, which is lower than the MHDCPLL and stays below 5% maximum limit allowed for such systems. Consequently, the AS $\varphi$ PLL is the most suitable candidate for grid-connected ESS to allow the flow of high

quality power to and from DC bus under distorted and faulty grid conditions.

In order to further verify and demonstrate the accurate performance and significance of proposed PLL, its impact on the grid-connected storage system (Fig. 1) is validated using dSPACE DS1202. The injected *d* and *q*-axis currents and the active/reactive power flowing (to and/or from the grid) are important factors to investigate under faulty grid conditions. The performance of the proposed synchronization is validated in Fig. 15 where the grid voltage contains harmonic and interharmonic (5% of 5<sup>th</sup> and 7.2<sup>th</sup> each) and is also subjected to a 20% voltage sag (similar to simulation results). The proposed technique enables the injection of high quality power and current by accurately estimating the grid information (phase and frequency) under abnormal grid conditions, justifying in this way its positive impact on the power quality enhancement of overall grid-connected system.

Fig. 15: Experimental validation of proposed technique for grid connected storage system under faults.

Hence, it is evident the proposed technique as most suitable candidate for grid connected energy storage systems under normal as well as abnormal grid conditions.

#### VII. CONCLUSIONS

This paper proposes a single-phase PLL technique able to work under harmonic, interharmonics, DC-offset and faulty grid conditions. The algorithm has lower complexity, resulting in fast and accurate estimation under grid frequency variations and presents a lower frequency overshoot. The effectiveness of the proposed PLL is validated by implementing it in the controller of grid-connected system, where it evidently improves the quality of injected current and power, and shows its superior performance and significant contribution towards the overall operation and stability of system. Consequently, the proposed  $AS\phi PLL$  is the most suitable candidate for grid-connected renewable and battery storage systems where it maintains the flow of high quality power under distorted and faulty grid conditions.

#### VIII. REFERENCES

- R. Teodorescu, M. Liserre, and P. Rodriguez, Grid converters for photovoltaic and wind power systems. Hoboken, NJ, USA: Wiley-IEEE Press, 2011.

- [2] N. Jabbour, E. Tsioumas, C. Mademlis, and E. Solomin, "A highly effective Fault-Ride-Through strategy for a wind energy conversion

- system with a doubly fed induction generator," *IEEE Transactions on Power Electronics*, vol. 35, pp. 8154-8164, 2020.

- [3] I. Serban and C. Marinescu, "Control strategy of three-phase battery energy storage systems for frequency support in microgrids and with uninterrupted supply of local loads," *IEEE Trans. Power Electronics*, vol. 29, pp. 5010-5020, 2014.

- [4] D.-I. Stroe, V. Knap, M. Swierczynski, A.-I. Stroe, and R. Teodorescu, "Operation of a grid-connected lithium-ion battery energy storage system for primary frequency regulation: A battery lifetime perspective," *IEEE transactions on industry applications*, vol. 53, pp. 430-438, Feb. 2017.

- [5] Z. Ali, N. Christofides, L. Hadjidemetriou, E. Kyriakides, Y. Yang, and F. Blaabjerg, "Three-phase phase-locked loop synchronization algorithms for grid-connected renewable energy systems: A review," *Renewable & Sustainable Energy Reviews*, vol. 90, pp. 434-452, July 2018.

- [6] U. Akram, M. Nadarajah, R. Shah, and F. Milano, "A review on rapid responsive energy storage technologies for frequency regulation in modern power systems," *Renewable and Sustainable Energy Reviews*, vol. 120, p. 109626, 2020.

- [7] S. Golestan, M. Monfared, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase grid-connected power conditioning systems," *IEEE Trans. Power Electronics*, vol. 27, pp. 3639-3650, 2012.

- [8] L. Liu, Y. Zhou, and H. Li, "Coordinated active and reactive power management implementation based on dual-stage PLL method for gridconnected PV system with battery," in *Proc. IEEE ECCE*, 2010, pp. 328-335.

- [9] Z. Ali, N. Christofides, L. Hadjidemetriou, and E. Kyriakides, "A computationally efficient current controller for simultaneous injection of both positive and negative sequences," in *Proc. IEEE ECCE Europe* 2017, pp. P.1-P.10.

- [10]K. Saleem, K. Mehran, and Z. Ali, "Online Reduced Complexity Parameter Estimation Technique for Equivalent Circuit Model of Lithium-ion Battery," *Electric Power System Research*, pp. 1-12, 2020.

- [11]K. Saleem, Z. Ali, and K. Mehran, "A single-phase synchronization technique for grid-connected RESS under distorted grid conditions," in 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 4665-4672.

- [12] Y. Yang, F. Blaabjerg, and Z. Zou, "Benchmarking of grid fault modes in single-phase grid-connected photovoltaic systems," *IEEE Trans. Industry Applications*, vol. 49, pp. 2167-2176, 2013.

- [13]Y. Yang, L. Hadjidemetriou, F. Blaabjerg, and E. Kyriakides, "Benchmarking of phase locked loop based synchronization techniques for grid-connected inverter systems," in *Proc. IEEE ECCE Asia*, 2015, pp. 2167-2174.

- [14]Y. Yang and F. Blaabjerg, "Synchronization in single-phase grid-connected photovoltaic systems under grid faults," in *Proc. IEEE PEDG*, Alborg, Denmark, 2012, pp. 476-482.

- [15]M. K. Ghartemani, S. A. Khajehoddin, P. K. Jain, and A. Bakhshai, "Problems of startup and phase jumps in PLL systems," *IEEE Trans. Power Electronics*, vol. 27, pp. 1830-1838, 2012.

- [16]J. Matas, M. Castilla, J. Miret, L. G. de Vicuña, and R. Guzman, "An adaptive prefiltering method to improve the speed/accuracy tradeoff of voltage sequence detection methods under adverse grid conditions," *IEEE Transactions on Industrial Electronics*, vol. 61, pp. 2139-2151, 2013.

- [17]S. A. Khajehoddin, M. Karimi-Ghartemani, A. Bakhshai, and P. Jain, "A power control method with simple structure and fast dynamic response for single-phase grid-connected DG systems," *IEEE Transactions on Power Electronics*, vol. 28, pp. 221-233, Jan 2013.

- [18] M. Saitou, N. Matsui, and T. Shimizu, "A control strategy of single-phase active filter using a novel d-q transformation," in *Proc. of IAS Annual Meeting*, Salt Lake City, USA, 2003, pp. 1222-1227.

- [19] S. Golestan, J. M. Guerrero, A. Vidal, A. G. Yepes, J. Doval-Gandoy, and F. D. Freijedo, "Small-signal modeling, stability analysis and design optimization of single-phase delay-based PLLs," *IEEE Trans. Power Electronics*, vol. 31, pp. 3517-3527, 2016.

- [20] B. Zhang, K. Zhou, and D. Wang, "Multirate repetitive control for PWM DC/AC converters," *IEEE Trans. Industrial Electronics*, vol. 61, pp. 2883-2890, 2014.

- [21]S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo, and M. Monfared, "Moving average filter based phase-locked loops: Performance

- analysis and design guidelines," *IEEE Trans. Power Electronics*, vol. 29, pp. 2750-2763, 2014.

- [22] Y. Han, M. Luo, J. Guerrero, and L. Xu, "Comparative performance evaluation of orthogonal-signal-generators-based single-phase PLL algorithms, a survey," *IEEE Trans. Power Electronics*, vol. 31, pp. 3932-3944, 2016.

- [23]F. Gonzalez-Espin, G. Garcera, I. Patrao, and E. Figueres, "An adaptive control system for three-phase photovoltaic inverters working in a polluted and variable frequency electric grid," *IEEE Trans. Power Electronics*, vol. 27, pp. 4248-4261, 2012.

- [24] K. Lee, J. Lee, D. Yoo, and H. Kim, "A novel grid synchronization PLL method based on adaptive low-pass notch filter for grid-connected PCS," *IEEE Trans. Industrial Electronics*, vol. 61, pp. 292-301, 2014.

- [25]L. Hadjidemetriou, E. Kyriakides, and F. Blaabjerg, "A robust synchronization to enhance the power quality of renewable energy systems," *IEEE Trans. Industrial Electronics*, vol. 62, pp. 4858-4868, Feb. 2015.

- [26]S. Golestan, J. M. Guerrero, and J. C. Vasquez, "A nonadaptive window-based pll for single-phase applications," *IEEE Transactions on Power Electronics*, vol. 33, pp. 24-31, Jan. 2018.

- [27]K. Saleem, K. Mehran, and Z. Ali, "An improved pre-filtering moving average filter based synchronization algorithm for single-phase V2G application," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 4088-4093.

- [28] A. Kulkarni and V. John, "Analysis of bandwidth-unit-vector-distortion tradeoff in PLL during abnormal grid conditions," *IEEE Trans. Industrial Electronics*, vol. 60, pp. 5820-5829, 2013.

- [29] Karimi Ghartemani, Masoud Khajehoddin, S Ali Jain, Praveen K Bakhshai, Alireza Mojiri, and Mohsen, "Addressing DC component in PLL and notch filter algorithms," *IEEE Transactions on Power Electronics*, vol. 27, pp. 78-86, 2011.

- [30]M. Ciobotaru, R. Teodorescu, and V. G. Agelidis, "Offset rejection for PLL based synchronization in grid-connected converters," in 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, 2008, pp. 1611-1617.

- [31]S. Shinnaka, "A robust single-phase PLL system with stable and fast tracking," *IEEE Transactions on Industry Applications*, vol. 44, pp. 624-633, 2008.

- [32]P. Rodríguez, A. Luna, I. Candela, R. Mujal, R. Teodorescu, and F. Blaabjerg, "Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid conditions," *IEEE Transactions on Industrial Electronics*, vol. 58, pp. 127-138, 2010.

- [33]B. Liu, M. An, H. Wang, Y. Chen, Z. Zhang, C. Xu, et al., "A simple approach to reject DC offset for single-phase synchronous reference frame PLL in grid-tied converters," *IEEE Access*, vol. 8, pp. 112297-112308, 2020.

- [34] L. Hadjidemetriou, E. Kyriakides, Y. Yang, and F. Blaabjerg, "Power quality improvement of single-phase photovoltaic systems through a robust synchronization method," in 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Sep, 2014, pp. 2625-2632.

- [35]L. Hadjidemetriou, E. Kyriakides, Y. Yang, and F. Blaabjerg, "A synchronization method for single-phase grid-tied inverters," *IEEE Trans. Power Electronics*, vol. 31, pp. 2139-2149, 2016.

- [36]Y. Yang, K. Zhou, H. Wang, F. Blaabjerg, D. Wang, and B. Zhang, "Frequency adaptive selective harmonic control for grid-connected inverters," *IEEE Transactions on Power Electronics*, vol. 30, pp. 3912-3924, 2014.